IEC TS 61945 pdf download

IEC TS 61945 pdf download Integrated circuits – Manufacturing line approval – Methodology for technology and failure analysis

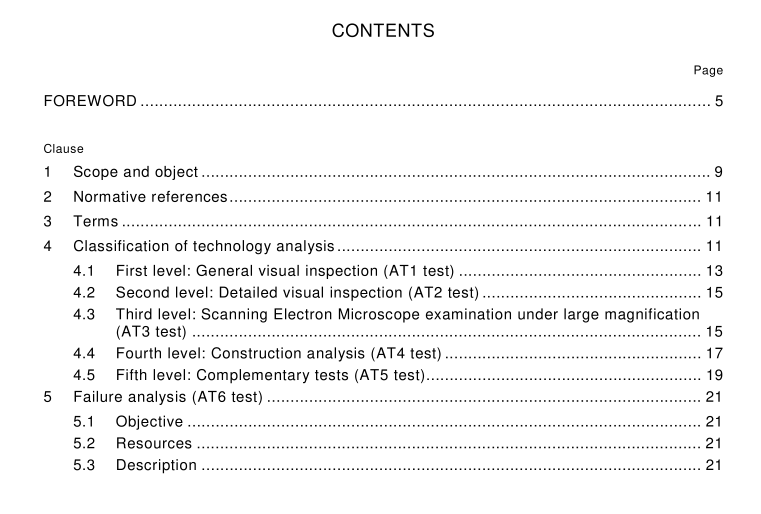

1Scope and object

This technical specification gives the methodology for technology and failure analysis inmanufacturing integrated circuits.

Taking into account the level of complexity of techniques and means to be used, the presenttechnical specification covers the classification of several levels of technology analysis thatmay be used for semiconductors and defines for each level:

– the objective to be performed (or goal);

– the points to be investigated;

– the tools and techniques needed for currently available technologies to perform these objectives.

Technology analysis is used to determine the way a component is built by observing it usingadequate resolution,which increases progressively with the level of analysis.

In addition,it allows detection of any fault potentially affecting the reliability of the devicesunder typical working conditions.

lt may be used to verify the conformance of a device to its manufacturing documents, but mayalso be used to determine the physical and chemical characteristics of the device under test.

The points observed during the analysis can also serve as guidelines for an expert in a futurequality audit of a manufacturing line.

By using similar or case-specific means, the failure analysis leads to identifying the physicalreasons of a failure found in a device during a test or during normal working conditions.

Through a deep knowledge of the component and of its intrinsic failure mechanisms, thetechnology analysis can prepare for future failure analyses.

This technical specification is considered as a suitable test methodology when referred to inan application document. Such documents shall indicate the specific conditions for itsapplication.

2 Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this Technical Specification. For dated references, subsequent amendments to, or revisions of, any of these publications do not apply. However, parties to agreements based on this Technical Specification are encouraged to investigate the possibility of applying the most recent editions of the normative documents indicated below. For undated references, the latest edition of the normative document referred to applies. Members of IEC and ISO maintain registers of currently valid International Standards.

IEC 60749:1 996, Semiconductor devices – Mechanical and climatic test methods

MIL STD 883

3 Terms

For the purpose of this technical specification, the following terms apply.

Reverse engineering: Electrical topology recognition of the circuit by identifying functional blocks and designing initial electrical and logic schematics.

RIE: Reactive ion etching.

SEM: Scanning electron microscope.